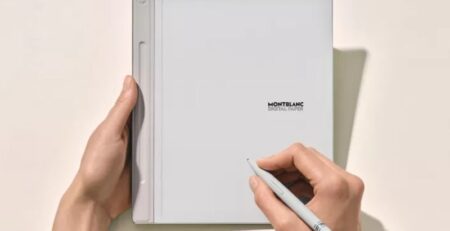

Método de Baixo Custo para Co-Empacotamento de Chips Fotônicos e Eletrônicos

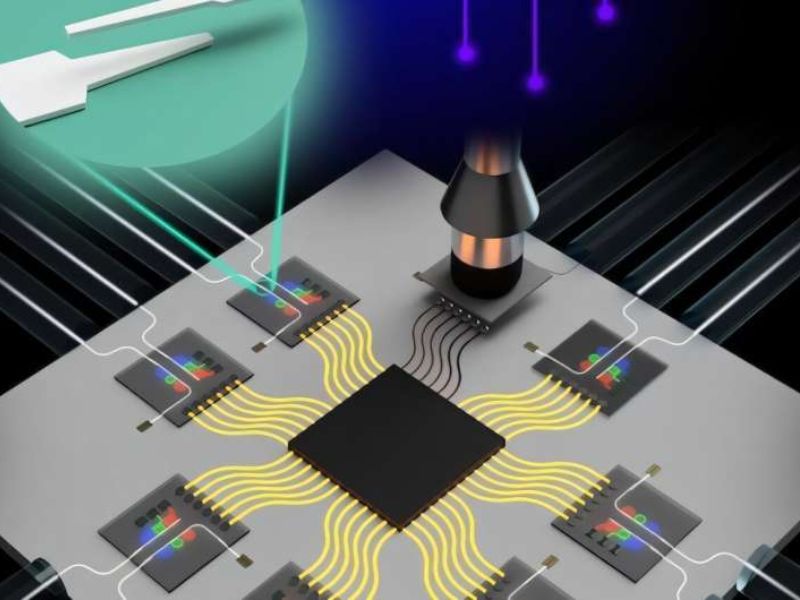

O dispositivo do MIT na legenda verde pode ser a chave para uma comunicação de dados mais rápida e energeticamente eficiente. Ele resolve um grande problema associado ao encapsulamento de um chip elétrico (preto, no centro) com chips fotônicos (os oito quadrados ao redor). Esta imagem também mostra uma ferramenta automatizada posicionando o chip fotônico final. Créditos da imagem: Drew Weninger, MIT.

A computação e as comunicações digitais caminham para um futuro que combina a eletrônica — processamento de dados usando eletricidade — com a fotônica, que utiliza a luz para a mesma finalidade. Essa integração pode permitir um fluxo global de dados muito maior, além de melhorar a eficiência energética.

“Em resumo, unir fotônica e eletrônica em um único encapsulamento é o equivalente ao transistor no século XXI. Sem esse avanço, o escalonamento futuro não será possível”, afirma Lionel Kimerling, Professor Thomas Lord de Ciência e Engenharia de Materiais do MIT e diretor do Centro de Microfotônica do MIT.

Inovação Sustentável na Cadeia de Produção de Microchips

O FUTUR-IC visa revolucionar a fabricação de microchips com soluções que economizam recursos

É aí que entra o FUTUR-IC — uma nova equipe de pesquisa sediada no MIT. “Nossa missão é desenvolver uma cadeia de valor para a indústria de microchips que utilize recursos de forma eficiente”, afirma Anu Agarwal, chefe do FUTUR-IC e principal cientista pesquisador do Laboratório de Pesquisa de Materiais (MRL).

Pesquisadores do FUTUR-IC, incluindo Anu Agarwal e Lionel Kimerling, desenvolveram um novo método para coempacotamento de chips fotônicos e eletrônicos que aborda as principais limitações das abordagens existentes. Um grande benefício é que os fabricantes podem usar ferramentas padrão e alinhamento passivo de baixo custo para produzir o dispositivo de forma mais econômica.

O dispositivo patenteado foi destaque na capa da Advanced Engineering Materials no início deste ano. Um artigo relacionado, do aluno do DMSE, Drew Weninger, ganhou o prêmio de Melhor Artigo de Estudante no 57º Simpósio Internacional de Microeletrônica, realizado no último outono.

Weninger, Kimerling, Agarwal, Serna (Bridgewater State) e Ranno (MIT) foram coautores do artigo.

Promovendo um Setor de Microchips Mais Eficiente em Recursos

Kimerling aponta que, até 2020, mais de 50 bilhões de dispositivos — incluindo celulares e sistemas de GPS — se conectarão à nuvem, impulsionando a demanda por data centers de grande porte. Enquanto isso, a quantidade de dados que flui por esses data centers aumenta mil vezes a cada década.

Esse aumento na comunicação consome energia. “E precisamos atender a essa demanda sem aumentar o uso de energia, já que a economia global não está crescendo tão rápido”, diz Kimerling, que também é filiado ao MRL. Para resolver isso, precisamos aumentar a produção de energia ou melhorar a eficiência energética da tecnologia da informação.

Imagens detalhando o processo de fabricação. Em a), o fluxo do processo usado para fabricar e encapsular os protótipos de acoplamento chip-a-chip. b), imagens SEM transversais mostram os tamanhos mínimo e máximo das características para o SOI e SiN 𝑥 . Em c,d), o protótipo chip-a-chip e o chip de vidro separado na fase de teste. e), um esquema da configuração de teste. Crédito: Advanced Engineering Materials (2024). DOI: 10.1002/adem.202402095

Integrando Fotônica e Eletrônica para Enfrentar a Crise Energética dos Microchips

A fusão da fotônica com a eletrônica encontrada nos microchips modernos pode ajudar a resolver problemas de eficiência energética, já que a transmissão de dados por meio da luz é muito mais eficiente em termos energéticos do que o uso de eletricidade. “Nosso princípio norteador é confiar na eletrônica para computação e na fotônica para comunicação a fim de gerenciar a crise energética”, explica Agarwal.

Mas essa abordagem apresenta obstáculos significativos.

Um grande desafio é o alto custo e a complexidade de conectar chips eletrônicos e fotônicos na mesma unidade. As fibras ópticas têm núcleos com apenas dez micrômetros de largura, enquanto os chips fotônicos têm seções transversais minúsculas — apenas 0,2 por 0,5 micrômetros — exigindo um alinhamento extremamente preciso para evitar a dispersão da luz. Atualmente, os técnicos precisam testar cada conexão individualmente com um laser para confirmar a transmissão adequada da luz.

“E com a crescente demanda por maior capacidade de dados, o número de conexões de fibra está aumentando rapidamente”, observou Weninger. “Este método de alinhamento ativo não será sustentável para escalabilidade no futuro.”

Maior Flexibilidade

O dispositivo recém-desenvolvido, conhecido como acoplador evanescente, facilita significativamente o desafio de alinhar fibras dentro de um sistema eletrônico-fotônico. “Os acopladores tradicionais dependem de um único ponto de acoplamento, o que exige um alinhamento extremamente preciso”, explica Agarwal. “Nosso acoplador, no entanto, apresenta uma região de interação mais longa, o que flexibiliza bastante esses requisitos de alinhamento.” Essa melhoria permite a montagem robótica passiva dos circuitos integrados, permitindo uma transmissão de luz mais eficiente sem a necessidade de alinhamento ativo a laser.

Outro avanço notável, de acordo com Ranno, é que o acoplador permite a transmissão vertical de luz entre as múltiplas camadas do chip. Este é um grande avanço, visto que guiar a luz para fora do plano horizontal costuma ser muito desafiador.

“Em eletrônica, mover elétrons entre camadas é simples”, diz Weninger. “Mas a luz não se curva naturalmente em ângulos agudos.” O novo design supera essa limitação, permitindo que sinais ópticos viajem entre chips empilhados.

Ranno resume: “Criamos um projeto de integração fotônica-eletrônica que é eficiente em termos de espaço, confiável, tolerante a variações de alinhamento e minimiza a perda de luz — essencialmente, ele preenche todos os requisitos para uma interconexão de alto desempenho.”

Este trabalho foi realizado em parte por meio do uso das instalações do MIT.nano e inclui contribuições do Consórcio de Empacotamento Eletrônico-Fotônico do MIT.

Leia o Artigo Original Tech Xplore

Leia mais Malásia Exigirá Aprovação Oficial para Comercializar Chips de IA Fabricados nos Estados Unidos